存算一体芯片迈进开源

Ai芯天下前言:

存算一体架构正受到学界、产界等各方的热议。

智能化时代的算力需求和计算服务业态正在发生变革的背景下,巨头IDM厂商和国内新锐的算力芯片厂商都在探索存算一体芯片,并衍生出不同的架构和技术路线。

作者?| 方文三

图片来源?|??网 络?

存算一体底层创新

目前市面上的芯片都是基于冯诺依曼架构,其特点是处理单元和存储单元分离,各不相干,需要运算的时候,计算单元再从存储单元读取数据进行处理,处理完再还回去。

而存算一体则是把存储单元和处理单元合二为一,去掉了中间传输路径,所以可以大幅减少数据搬运,消过程中不必要的延迟和功耗,能耗可降至 1/10-1/100,能效可提升 10-100TOPS/W。

因为存储一体是以存储器为介质,在里面加入计算单元,所以可以直接利用存储单元进行逻辑计算提升算力,在特定区域可提供 1000TOPS 以上的算力。

存算一体芯片目前发展难点

传统架构是计算和存储相分离,现在两者要合二为一,这就对存储器本身和存算一体的设计提出更高的要求,是需要技术人员从头探索的新领域。

基于存算一体是把计算和数据高度耦合,因此一旦其中一方出问题,另一方几乎也会遭到极大影响,这都是需要处理的难题。

其中最重要一点便是生态与编程框架不完善,缺乏相应的指令集与软件工具。

一方面,各单位、公司开发的存算一体芯片均基于自行定义的编程接口,缺乏统一的编程接口,造成了存算一体软件生态的分散,不同厂商开发的上层软件无法互相通用,极大的影响了存算一体芯片的大规模使用。

另一方面,除了高效的硬件设计,神经网络模型面向存算一体架构时,计算任务如何映射、调度,也是发挥神经网络加速器性能和能效的关键。

存算一体国内外玩家盘点

存算一体技术可有效突破芯片性能瓶颈,是解决算力提升放缓和算力需求快速增长之间尖锐矛盾的一种关键技术路径,目前存算技术正处在从学术到工业产品的跃迁的关键时期。

三星

三星2021年2月发布HBM2-PIM,将4片常规DRAM die和4片具有计算功能的DRAM die通过TSV通孔垂直组合在一起。其中具有计算功能的DRAM die内部集成了计算逻辑单元,即将A引擎引入每人存储子单元,从而将处理操作转移到HBM。每个存储子单元都有一个嵌入式可编程计算单元(PCU) ,其运行频率为300 MHz,每个裸片上 (PIM-DRAM die) 有32个PCU。

Mythic

Mythic2021年5月获得 7000 万美元的 C 轮融资,累计融资金额1.652 亿美元产品特点: 基于区块的A 计算架构一一内存计算、数据流架构和模拟计算。

2021年6月发布由72个AMP切片构成,每个切片内部集成一系列闪存单元、ADC阵列、1个32位RISC纳米处理器、1个16位SIMD矢量处理器、SRAM和1个片上网络 (NOC) 路由器,算力达25TOPS。

阿里达摩院

达摩院研发的存算一体芯片是全球首次采用混合键合(Hybrid Bonding)的 3D 堆叠技术,将计算芯片和存储芯片 face-to-face 地用特定金属材质和工艺进行互联。

得益于整体架构的创新,达摩院的存算一体AI芯片同时实现了高性能和低系统功耗。

在实际推荐系统应用中,相比传统CPU计算系统,该芯片的性能提升10倍以上,能效提升超过300倍。

后摩智能

后摩智能由吴强博士与多位国际顶尖学者和芯片工业界资深专家联合组建,是全球存算一体智驾芯片的先行者。

后摩智能发布了首款存算一体芯片——鸿途 H30,最高物理算力 256TOPS,功耗仅为 35W,碾压国内一众智驾芯片。

苹芯科技

苹芯科技已开发实现多款基于SRAM的存内计算加速单元,致力于为人工智能行业提供了低成本、高效率、低能耗、高性能的芯片解决方案。

与此同时,面向多元化的场景,公司也正在开发利用新型存储器为底层技术,为客户提供便捷的AI硬件加速方案。

此方向突破了传统冯·诺伊曼架构所带来的局限,可广泛应用于众多人工智能行业领域,包括但不限于智慧城市、智能家居、工业物联网,以及各类智慧终端、可穿戴设备、自主无人系统等领域。

知存科技

知存科技专注存内计算芯片领域,创新使用Flash存储器完成神经网络的储存和运算,解决AI的存储墙问题,提高运算效率,降低成本。

公司旗下WTM2101芯片适配低功耗AIoT应用,可使用微瓦到毫瓦级功耗完成大规模深度学习运算,可应用于智能语音、智能健康等市场领域,目前已完成批量生产和市场应用。WTM8系列芯片面向6-48Tops算力产品,应用于4K-8K视频的实时处理。

存算一体芯片市场前景

存内计算的发展类似于存储器的发展路径,算力每年可以有5-10倍提升,能效每年会有1-2倍提升,成本每年会有30-50%下降,能把成本、算力、能效都可以做到最优。

中早期的存算一体芯片算力较小,更多地应用在对低功耗和高能效有强烈需求的端侧场景,比如智能家居场景下的智能语音和轻量级视觉层面的应用。

但存算一体芯片算力不断提升,其使用范围逐渐扩展到边缘端以及云端的大算力应用领域。

智能驾驶技术的迭代升级,智能汽车对算力的需求越来越大;并且,智能汽车作为一个边缘端设备,相比云端,对成本和功耗更为敏感。

存算一体技术通过将计算功能和存储功能有机融合,可有效降低甚至消除数据频繁搬运带来的功耗问题,并且能够在不依赖于先进工艺的情况下,做出大算力芯片,能够同时兼顾能效和成本,可破解当前传统架构大算力AI芯片的所面临的一些困局。

也是智能驾驶场景下被业内人士迫切期待的一种高能效AI芯片架构的技术实现路径。

存算一体芯片开源指令集和编译器

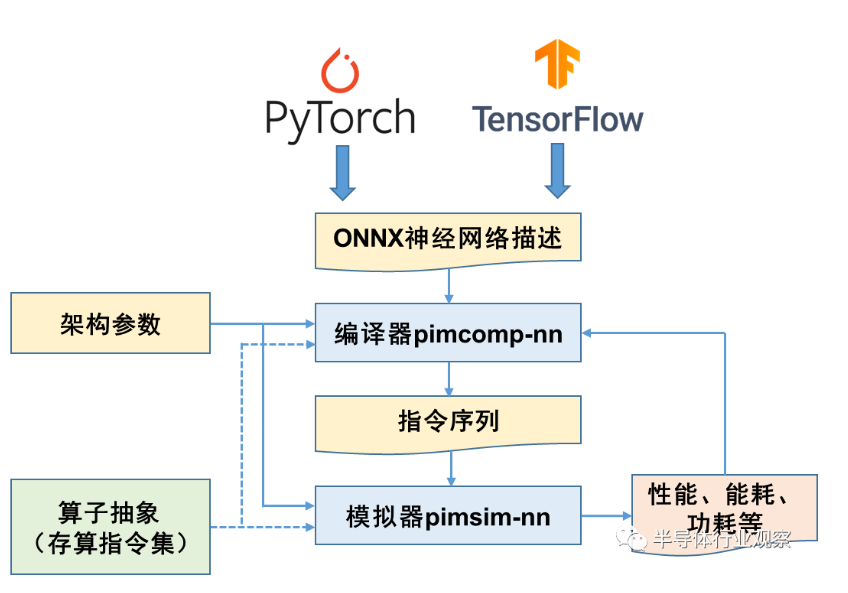

在今年的集成电路EDA领域顶级会议上,中国科学院计算技术研究所智能计算机中心陈晓明和韩银和研究员团队发表论文,公布了一项新的研究成果:PIMCOMP-NN存算一体通用编译器和PIMSIM-NN——存算一体通用模拟器,二者基于一套之前该团队开源的存算一体指令集,构成了完整的开源存算一体工具链,该项工作或将为存算一体芯片建立统一的生态做出一定的贡献。

该工具链建立在一套面向神经网络的存算一体指令集基础上。

指令集作为芯片软硬件设计的接口,对于软件生态有着举足经重的作用,为了使工具链对多种多样的存算一体芯片的底层操作具有通用性,该课题组首先抽象了存算一体架构支持的基本算子,定义了一套统一的面向神经网络的存算一体指令集。

随着开源理念在存算一体领域的拓展,将有助于行业建立统一的编程和接口标准,从而使来自不同厂商和研究机构的产品实现互通。

这一标准化进程将有助于解决目前存算一体芯片领域的碎片化问题,提高生态系统的协同效率。

进一步推动存算一体芯片更容易与人工智能、大数据、物联网等产业相结合,形成更加丰富和复杂的应用场景。

结尾:

随着矛盾不断升级,高通和Arm破镜难圆已成定局。

对Arm公司来说,上有PC端巨擘X86的竞争压力,下有RISC-V欲取而代之;

再加上昔日盟友高通这一肘腋之患,重重隐忧正在动摇ARM在芯片产业下游的统治基础。

部分资料参考:热点微评:《ARM霸权下:高通的叛逃与国产厂商的无奈》,三易生活:《骁龙8 Gen4或全面换用自研架构,ARM不乐意了》, 谈芯说科技:《人工智能突飞猛进,ARM是否会掉队?》